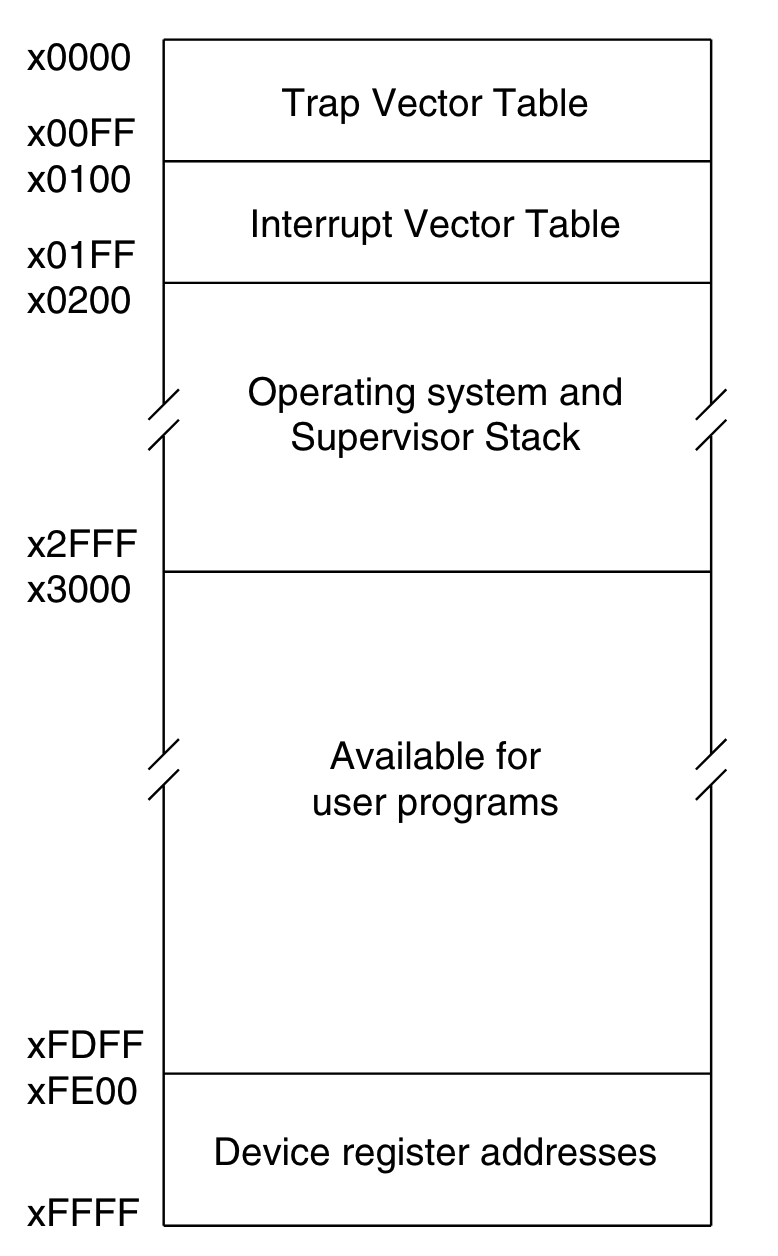

Interrupt vector table in RH850 F1KM family - Forum - RH850 & RL78F MCU - Renesas Engineering Community

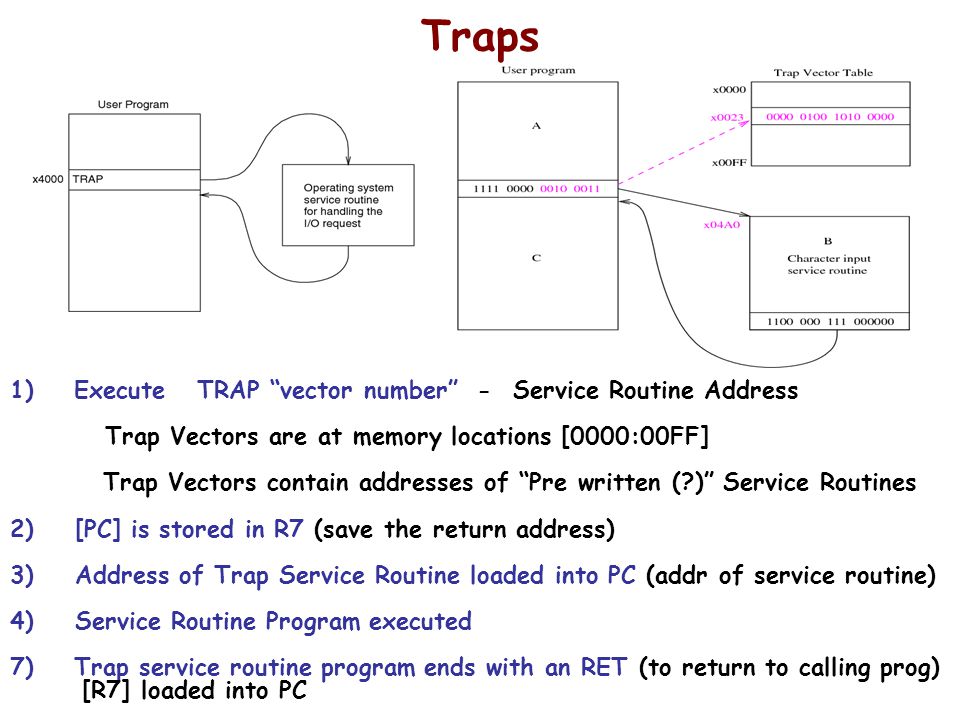

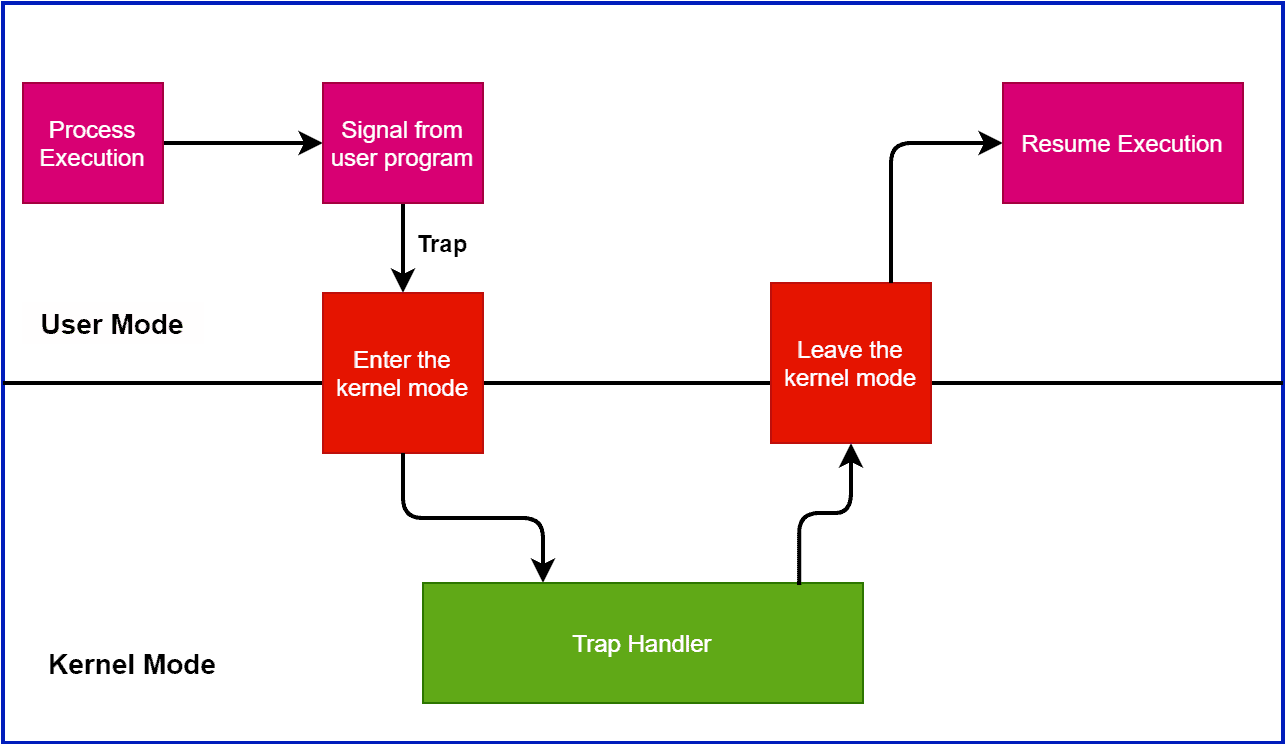

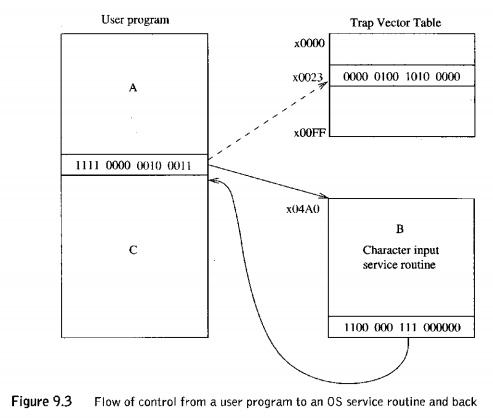

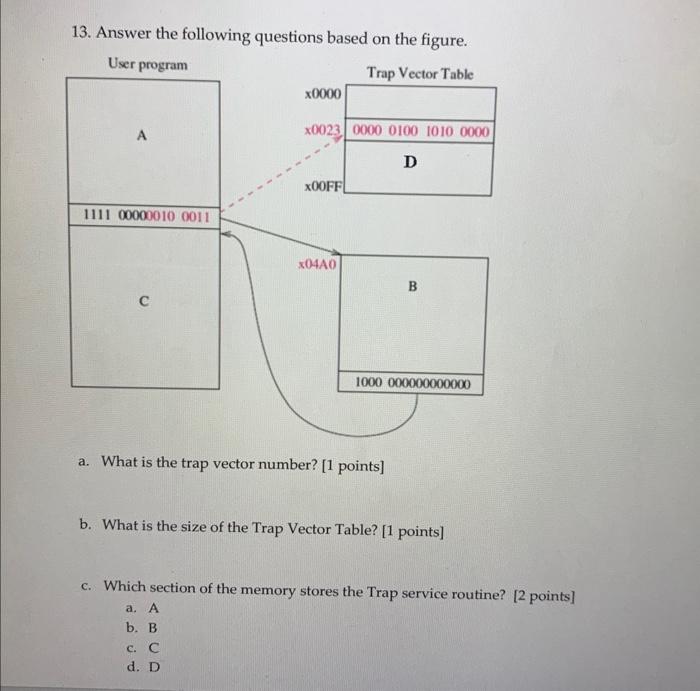

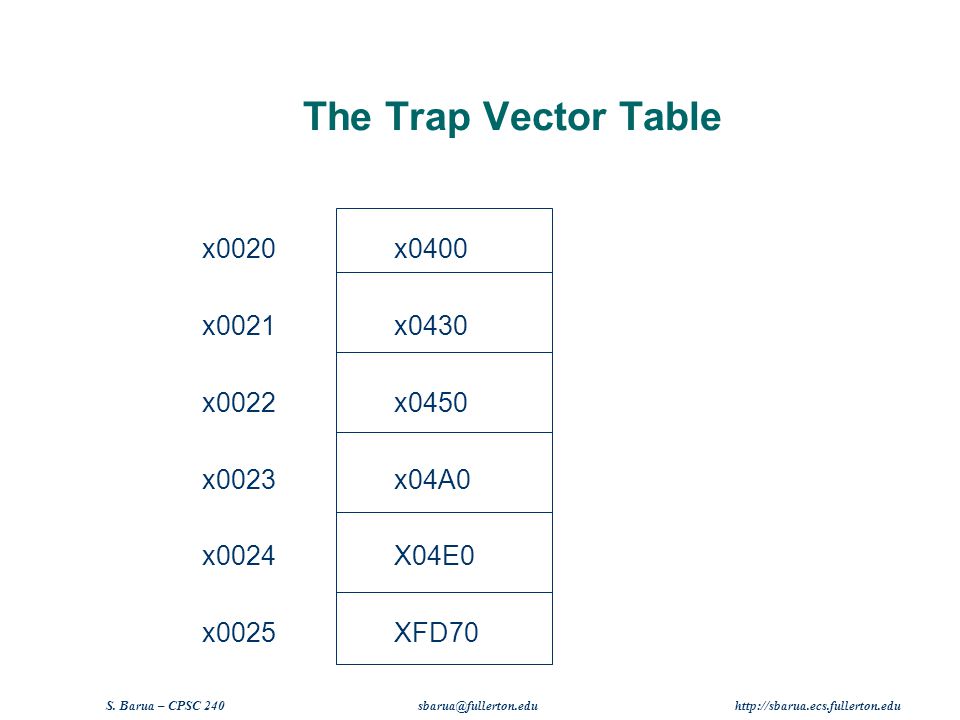

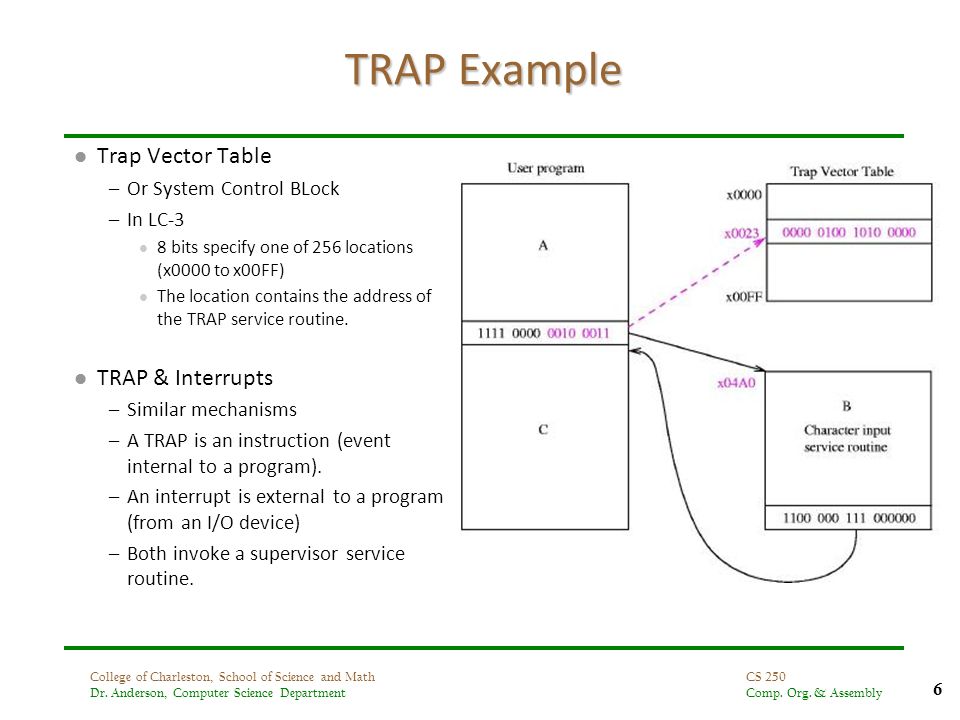

S. Barua – CPSC 240 CHAPTER 9 TRAP ROUTINES AND SUBROUTINES The TRAP mechanism allows the user program. - ppt download

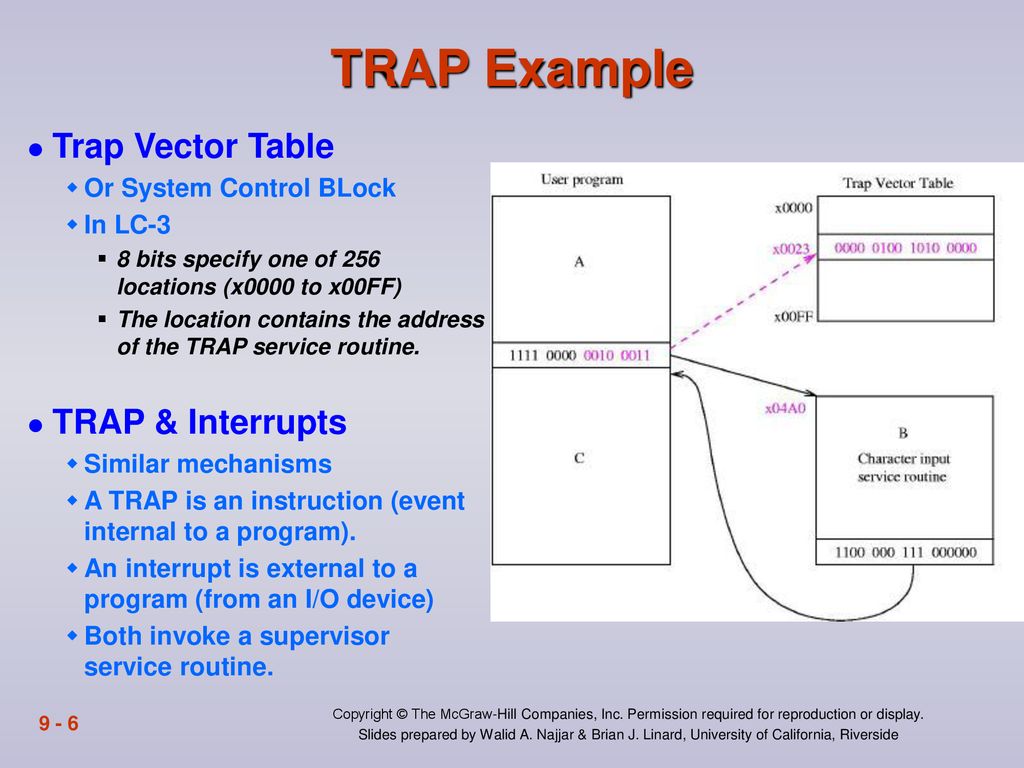

Chapter 9 Chapter 9 Subroutines and TRAPs l Privileged Instructions l TRAP Routines l Subroutines. - ppt download